——Delde fan DWIN Froum

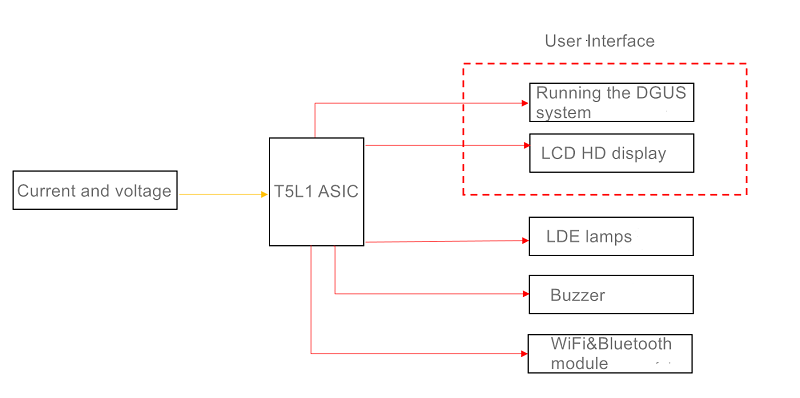

It brûken fan DWIN T5L1-chip as de kontrôlekearn fan 'e heule masine, ûntfangt en ferwurket touch, ADC-akwisysje, PWM-kontrôleynformaasje, en rydt it 3.5-inch LCD-skerm om de aktuele status yn realtime te werjaan.Stypje oanpassing op ôfstân fan LED-ljochtboarnehelderheid fia WiFi-module, en stypje stimalarm.

Programma funksjes:

1. Adopte T5L-chip om op hege frekwinsje te rinnen, AD analoge sampling is stabyl, en de flater is lyts;

2. Support TYPE C direkt ferbûn oan PC foar debuggen en programma baarnende;

3. Stypje hege snelheid OS core ynterface, 16bit parallel haven;UI-kearn PWM-poarte, AD-poarte lead out, goedkeap applikaasje-ûntwerp, gjin needsaak om ekstra MCU ta te foegjen;

4. Stypje WiFi, Bluetooth remote control;

5. Stypje 5 ~ 12V DC breed spanning en breed berik ynput

1.1 Skema diagram

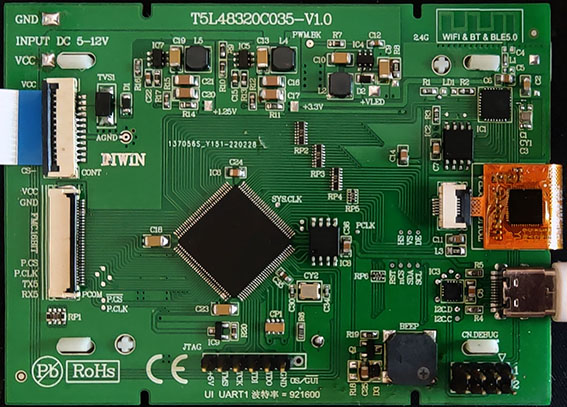

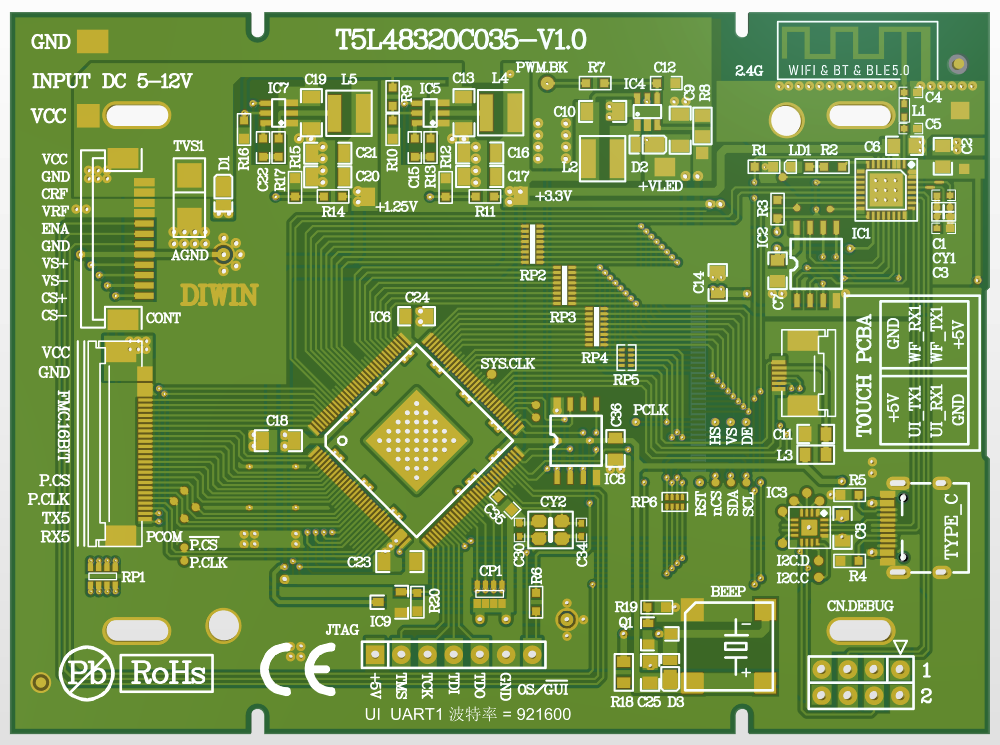

1.2 PCB board

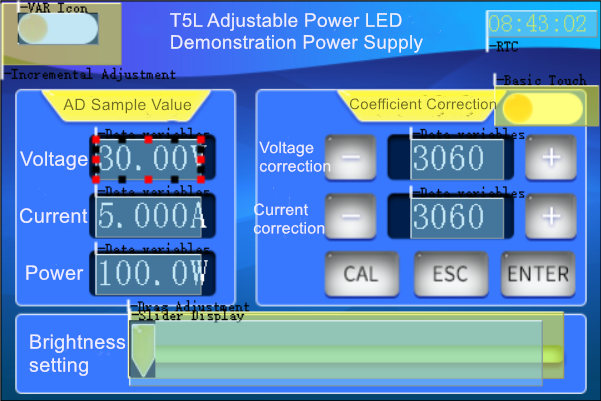

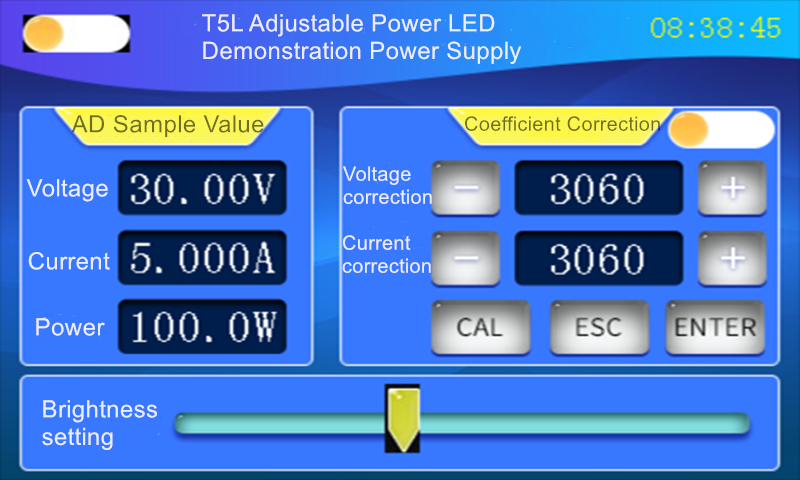

1.3 Brûkersynterface

Skamte yntroduksje:

(1) Hardware circuit design

1.4 T5L48320C035 circuit diagram

1. MCU logyske voeding 3.3V: C18, C26, C27, C28, C29, C31, C32, C33;

2. MCU core Netzteil 1.25V: C23, C24;

3. MCU analoge Netzteil 3.3V: C35 is de analoge Netzteil foar MCU.By typesetting, de kearn 1.25V grûn en de logyske grûn kinne wurde kombinearre tegearre, mar de analoge grûn moat wurde skieden.De analoge grûn en de digitale grûn moatte wurde sammele by de negative poal fan de LDO útfier grutte capacitor, en de analoge positive poal moat ek wurde sammele op de positive poal fan de LDO grutte capacitor, sadat AD sampling Noise wurdt minimalisearre.

4. AD analoge sinjaal oanwinst circuit: CP1 is de AD analoge ynfier filter capacitor.Om de samplingflater te ferminderjen, wurde de analoge grûn en digitale grûn fan 'e MCU ûnôfhinklik skieden.De negative poal fan CP1 moat wurde ferbûn mei de analoge grûn fan 'e MCU mei minimale impedânsje, en de twa parallelle capacitors fan' e kristal oscillator binne ferbûn mei de analoge grûn fan 'e MCU.

5. Buzzer circuit: C25 is de macht oanbod capacitor foar de buzzer.De buzzer is in induktyf apparaat, en d'r sil in peakstream wêze by operaasje.Om de peak te ferminderjen, is it nedich om de MOS-drivestream fan 'e buzzer te ferminderjen om de MOS-buis yn' e lineêre regio te wurkjen, en it circuit te ûntwerpen om it te meitsjen yn 'e skeakelmodus.Tink derom dat R18 parallel oan beide úteinen fan 'e buzzer moat wurde ferbûn om de lûdskwaliteit fan' e buzzer oan te passen en de buzzer skerp en noflik te meitsjen.

6. WiFi circuit: WiFi chip sampling ESP32-C, mei WiFi + Bluetooth + BLE.Op 'e bedrading binne de RF-krêftgrûn en de sinjaalgrûn skieden.

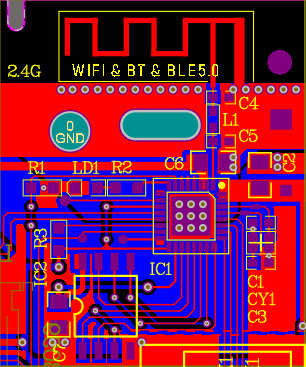

1.5 WiFi circuit design

Yn 'e boppesteande figuer is it boppeste diel fan' e koperen coating de macht grûn lus.De WiFi-antenne-refleksjegrûnlus moat in grut gebiet hawwe nei de krêftgrûn, en it sammelpunt fan 'e krêftgrûn is de negative poal fan C6.In reflektearre stroom moat wurde levere tusken de krêftgrûn en de WiFi-antenne, dus d'r moat koperen coating wêze ûnder de WiFi-antenne.De lingte fan 'e koperen coating is grutter as de útwreidingslingte fan' e WiFi-antenne, en de útwreiding sil de gefoelichheid fan 'e WiFi ferheegje;punt op de negative poal fan C2.In grut gebiet fan koper kin it lûd beskermje dat feroarsake wurdt troch de strieling fan de WiFi-antenne.De 2 koperen grûnen wurde skieden op 'e ûnderste laach en sammele nei it middelste pad fan ESP32-C troch fias.De RF-krêftgrûn hat in legere impedânsje nedich dan de sinjaalgrûnlus, dus d'r binne 6 fias fan 'e krêftgrûn nei it chippad om in genôch lege impedânsje te garandearjen.De grûn lus fan 'e kristal oscillator kin net hawwe RF macht streamend troch it, oars de kristal oscillator sil generearje frekwinsje jitter, en de WiFi frekwinsje offset sil net by steat wêze om te ferstjoeren en ûntfange gegevens.

7. Backlight LED Netzteil circuit: SOT23-6LED driver chip sampling.De DC / DC-voeding oan 'e LED foarmet ûnôfhinklik in lus, en de DC / DC-grûn is ferbûn mei de 3.3V LOD-grûn.Sûnt de PWM2-poartekearn is spesjalisearre, jout it in 600K PWM-sinjaal út, en in RC wurdt tafoege om de PWM-útfier te brûken as in ON / OFF-kontrôle.

8. Voltage input berik: twa DC / DC step-downs binne ûntwurpen.Tink derom dat de R13 en R17 wjerstannen yn 'e DC / DC circuit kin net weilitten.De twa DC / DC-chips stypje oant 18V-ynfier, wat handich is foar eksterne stroomfoarsjenning.

9. USB TYPE C debug haven: TYPE C kin wurde ynstutsen en unplugged foarút en efterút.Foarút ynfoegje kommunisearret mei de WIFI-chip ESP32-C om de WIFI-chip te programmearjen;omkearde ynfoegje kommunisearret mei de XR21V1410IL16 om de T5L te programmearjen.TYPE C stipet 5V Netzteil.

10. Parallel haven kommunikaasje: T5L OS kearn hat in protte frije IO havens, en 16bit parallel haven kommunikaasje kin wurde ûntwurpen.Kombinearre mei ST ARM FMC parallel haven protokol, it stipet syngroane lêzen en skriuwen.

11. LCM RGB hege snelheid ynterface design: T5L RGB útfier is direkt ferbûn oan LCM RGB, en buffer ferset wurdt tafoege yn 'e midden te ferminderjen LCM wetter rimpel ynterferinsje.By wiring, ferminderje de lingte fan 'e RGB-ynterfaceferbining, benammen it PCLK-sinjaal, en fergrutsje de RGB-ynterface PCLK, HS, VS, DE testpunten;de SPI-poarte fan it skerm is ferbûn mei de P2.4 ~ P2.7-poarten fan 'e T5L, wat handich is foar it ûntwerpen fan it skermbestjoerder.Lead RST, nCS, SDA, SCI testpunten om de ûntwikkeling fan 'e ûnderlizzende software te fasilitearjen.

(2) DGUS ynterface

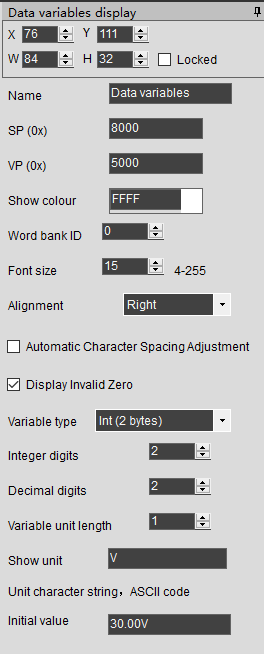

1.6 Data fariabele display kontrôle

(3) OS

//———————————DGUS lês- en skriuwformaat

typedef struktuer

{

u16 adr;//UI 16bit fariabele adres

u8 datLen;//8bitdata lingte

u8 *pBuf;//8bit gegevens oanwizer

} UI_packTypeDef;//DGUS lês en skriuw pakketten

//——————————-gegevens fariabele werjefte kontrôle

typedef struktuer

{

u16 VP;

u16 x;

u16 y;

u16 Kleur;

u8 Lib_ID;

u8 FontSize;

u8 Algnment;

u8 YntNum;

u8 DecNum;

u8 type;

u8 LenUint;

u8 StringUinit[11];

} Number_spTypeDef;// data fariabele beskriuwing struktuer

typedef struktuer

{

Number_spTypeDef sp;// define SP beskriuwing pointer

UI_packTypeDef spPack;// definiearje SP fariabele DGUS lêzen en skriuwen pakket

UI_packTypeDef vpPack;// define vp fariabele DGUS lês- en skriuwpakket

} Number_HandleTypeDef;// data fariabele struktuer

Mei de foarige gegevens fariabele handle definysje.Definiearje dêrnei in fariabele foar de werjefte fan spanningssampling:

Number_HandleTypeDef Hsample;

u16 voltage_sample;

Fier earst de inisjalisaasjefunksje út

NumberSP_Init(&Hsample,voltage_sample,0×8000);//0×8000 hjir is de beskriuwing pointer

//——Gegevensfariabele mei inisjalisaasje fan SP-oanwizerstruktuer——

void NumberSP_Init (Number_HandleTypeDef *number,u8 *wearde, u16 numberAddr)

{

number->spPack.addr = numberAddr;

number->spPack.datLen = sizeof(number->sp);

number->spPack.pBuf = (u8 *)&number->sp;

Read_Dgus(&number->spPack);

number->vpPack.addr = number->sp.VP;

switch(number->sp.Type) //De gegevenslingte fan 'e vp-fariabele wurdt automatysk selektearre neffens it gegevensfariabeletype ûntwurpen yn 'e DGUS-ynterface.

{

gefal 0:

gefal 5:

number->vpPack.datLen = 2;

brekke;

gefal 1:

gefal 2:

gefal 3:

gefal 6:

number->vpPack.datLen = 4;

gefal 4:

number->vpPack.datLen = 8;

brekke;

}

number->vpPack.pBuf = wearde;

}

Nei inisjalisaasje is Hsample.sp de beskriuwing pointer fan de spanning sampling data fariabele;Hsample.spPack is de kommunikaasje pointer tusken de OS kearn en de UI spanning sampling data fariabele fia de DGUS ynterface funksje;Hsample.vpPack is it attribút fan it feroarjen fan de spanning sampling gegevens fariabele, lykas lettertype Kleuren, ensfh wurde ek trochjûn oan de UI kearn troch de DGUS ynterface funksje.Hsample.vpPack.addr is de spanning sampling gegevens fariabele adres, dat is automatysk krigen fan de inisjalisaasje funksje.As jo feroarje it fariabele adres of fariabele gegevens type yn de DGUS ynterface, der is gjin needsaak om te fernijen de fariabele adres yn de OS kearn syngroan.Neidat de OS-kearn de voltage_sample-fariabele berekkent, hoecht it allinich de funksje Write_Dgus (& Hsample.vpPack) út te fieren om it te aktualisearjen.D'r is net nedich om de voltage_sample te pakken foar DGUS-oerdracht.

Post tiid: Jun-15-2022